- 만약 큰 데이터 블록을 전송하는 경우 CPU가 그 동작들을 수행하는데 많은 시간을 소모해야 하며, 시스템 버스도 대부분의 시간 동안 그러한 I/O 동작들을 위해 사용될 수 밖에 없는데, 이 문제점을 해결하기 위하여 직접기억장치액세스(Direct Memory Access:DMA)가 널리 사용되고 있다.

- DMA란 CPU의 개입 없이 I/O 장치와 기억장치 사이에 데이터 전송을 수행하는 매커니즘을 말한다.

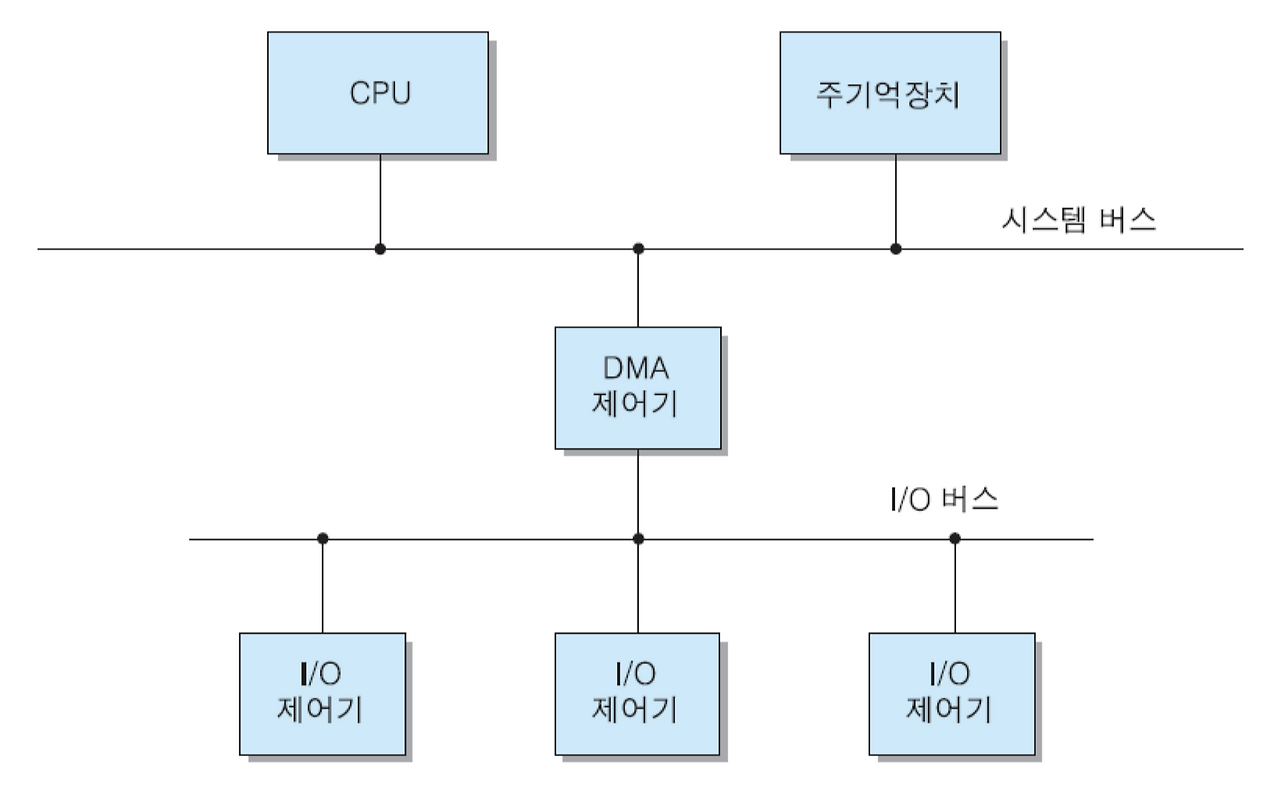

- DMA 방식을 사용하기 위해 시스템 버스에 DMA 제어기가 추가되어야 한다.

DMA 제어기

- CPU 개입 없이 I/O 장치와 기억장치 간의 데이터 전송을 수행하는 DMA 동작을 지원하는 하드웨어 모듈이다.

주기억장치의 데이터를 I/O 장치로 내보내거나 (I/O write), I/O 장치로부터 데이터를 주기억장치로 읽어들일 때(I/O read) CPU는

DMA 제어기로 다음과 같은 정보들이 포함된 명령을 보낸다.

- I/O 장치의 주소

- 연산(쓰기 혹은 읽기) 지정자

- 데이터가 읽혀지거나 쓰여질 주기억장치 영역의 시작 주소

- 전송될 데이터 단어들의 개수

여기서 I/O 장치가 디스크인 경우 주소가 디스크 드라이브 번호, 트랙(혹은 실린더) 번호 및 섹터 번호를 모두 포함해야 한다.

- CPU는 이러한 정보들이 포함된 명령을 DMA 제어기로 보낸 다음에는 다른 일을 계속 한다.

- CPU는 I/O 동작을 DMA 제어기에 맡기고, 모든 데이터 전송 동작이 완료될 때까지 전혀 개입하지 않는다.

- DMA 제어기가 DMA 동작을 수행하기 위해서는 시스템 버스를 통하여 주기억장치를 액세스하게 된다. 즉, CPU 와 DMA 제어기가 시스템 버스를 공유하는 것이다.

- DMA 제어기는 가능한 한 CPU의 정상적인 동작을 방해하지 않으면서 시스템 버스를 사용한다. 즉, PCU가 시스템 버스를 사용하지 않는 시간(ex) CPU가 내부적으로 명령어를 해독하거나 ALU 연산을 수행하는 시간 동안에 시스템 버스를 사용한다.

- 이 이유로 인해 DMA를 사이클 스틸링(cycle stealing)이라고도 부른다.

사이클 스틸링

- CPU가 시스템 버스를 사용하지 않는 동안에 DMA 제어기가 버스를 사용한다는 것을 의미하는 용어

- 큰 데이터 블록을 전송하는 경우에 그러한 사이클만 이용하게 되면, I/O 처리 시간이 너무 길어지게 된다. 따라서 일반적으로는 DMA 제어기가 시스템 버스 사용을 요구하면, PCU는 현재 사이클이 끝나는 즉시 사용 허가를 해주어서 DMA 동작이 신속하게 일어날 수 있도록 해주며, 그 동안에 CPU는 기다린다.

- DMA 제어기는 데이터를 한 번에 한 개씩 이동시킨 다음에 시스템 버스를 CPU에게 되돌려준다. 그리고 그러한 동작을 모든 데이터 블록을 전송할 때까지 반복한다.

DMA 제어기가 CPU에게 버스 사용을 요구하는 신호를 버스 요구(BUS REQ) 신호라고 하며, PCU가 DMA 제어기에 버스 사용을 허가하는 신호를 버스 승인(BUS GRANT) 신호라고 한다. 그리고 DMA 동작이 완료되면 DMA 제어기는 CPU로 인터럽트 요구(INTR) 신호를 보내어 그 사실을 알리며, CPU는 그에 따른 다음 절차를 진행하게 된다.

ex) 주기억장치 내의 어떤 데이터 블록을 디스크에 저장히기 위한 DMA 동작의 처리 순서

- CPU가 DMA 제어기에게 명령을 보낸다.

- DMA 제어기는 CPU로 BUS REQ 신호를 보낸다.

- CPU는 DMA 제어기로 BUS GRANT 신호를 보낸다.

- DMA 제어기가 버스를 사용하여 주기억장치로부터 데이터를 읽어서 디스크 제어기로 보낸다. (디스크에 저장)

- 저장할 데이터가 남아있다면, 2번부터 4번까지 다시 반복한다.

- 모든 데이터들의 저장이 완료되면, CPU로 INTR 신호를 보낸다.

- 위 그림을 보면 DMA 명령에 포함되는 내용들을 저장하는 레지스터들이 있다. 즉, I/O 장치의 주소를 저장하는 주소 레지스터와 데이터 버퍼 역할을 하는 데이터 레지스터, 그리고 전송될 데이터 수를 저장하는 카운터 레지스터 등이 있다.

- 이들은 I/O 제어기와 마찬가지로 각각 별도의 주소를 할당받으며, CPU는 그 주소를 이용하여 레지스터들을 액세스한다. 그리고 각종 제어 신호들을 발생하거나 받아들이기 위한 제어 회로들이 있다.

- DMA 동작은 주기억장치와 I/O 제어기 사이에 데이터를 한 번에 한 개씩 전송시키는데, DMA 제어기가 포함된 시스템 구성도의 이미지를 보면 그 때마다 시스템 버스를 두 번씩 사용한다.

- ex) 디스크 쓰기 동작을 위해 주기억장치의 데이터를 디스크 제어기로 전송하는 경우를 고려하면, 먼저 데이터를 주기억장치로부터 DMA 제어기로 이동시키기 위하여 시스템 버스를 한 번 사용하며, DMA 제어기로부터 데이터를 디스크 제어기로 이동시키기 위하여 다시 시스템 버스를 사용한다. 따라서 1024바이트 크기의 데이터 블록을 저장한다면, 시스템 버스를 모두 2048번 사용하게 된다.

- 결과적으로 DMA 동작을 위하여 시스템 버스가 너무 많이 사용되어 전체 시스템 성능이 저하된다.

- 이러한 문제를 해결하기 위한 방법은 DMA 제어기를 이용한 I/O 접속 방법을 이용하는 것이다.

- I/O 제어기를 시스템 버스에 직접 접속하는 것이 아닌 DMA 제어기에 접속하는 것이다. 이 경우ㅡ DMA 제어기가 데이터를 I/O 제어기로(부터) 이동시킬 때는 시스템 버스를 사용할 필요가 없다.

- 따라서 1024바이트 블록을 DMA로 전송하는 데 시스템 버스를 1024번만 사용하면 된다.

- 그런데, 각 DMA 제어기에 직접 접속할 수 있는 I/O 제어기의 수가 제한된다. 따라서 다양한 종류의 많은 I/O 장치들을 포함하고 있는 시스템에서는 여러 개의 DMA 제어기들을 시스템 버스에 접속해야 한다.

이러한 문제를 개선한 것은 I/O 버스를 이용한 DMA 구성도 이다.

- 이 구성에서 DMA 제어기가 시스템 버스와 I/O 버스 사이에 위치한다. 그리고 I/O 버스에는 각종 I/O 장치들이 제어기를 통하여 접속된다.

- 즉, 하나의 DMA 제어기가 I/O 버스를 통하여 여러 I/O 장치들을 위한 DMA 동작들을 지원하는 것이다.

이 경우 DMA 제어기의 내부에 I/O 버스 인터페이스 회로가 추가되어야 한다.

- I/O 장치들은 종류와 속도가 다양하고 제어 방법도 복잡하기 때문에, 간단한 구조를 가진 DMA 제어기로 지원하는 데는 한계가 있다.

- 디스크 쓰기 혹은 읽기 동작의 경우 데이터 블록의 크기가 512바이트 이상이기 때문에 그 데이터들은 버퍼링(임시 저장)하기 위한 내부 기억장치가 필요하다.

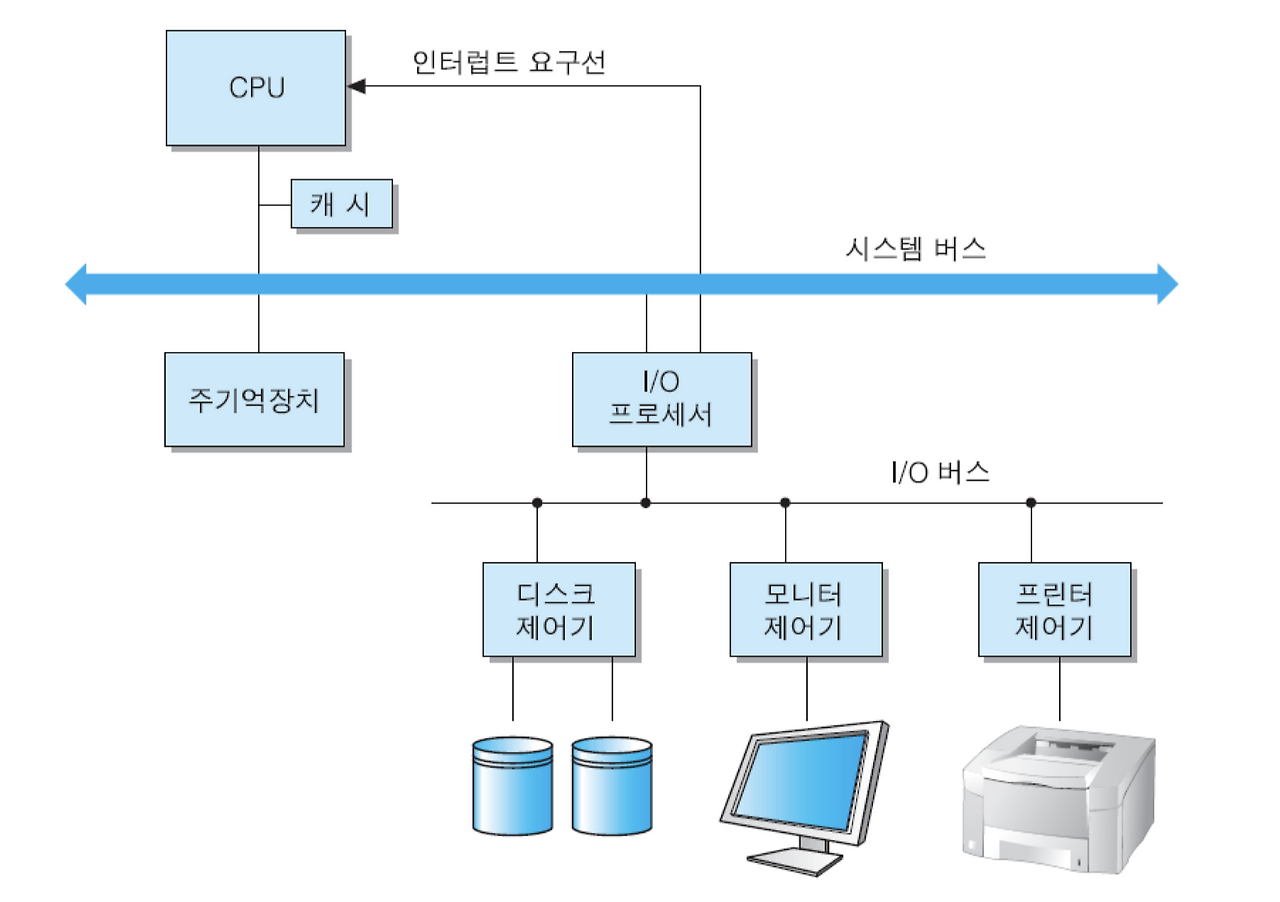

이러한 문제점들을 해결하기 위해 최근의 고성능 컴퓨터 시스템들에서는 DMA 제어기를 확장시킨 I/O 프로세서(I/O Processor: IOP)를 사용하고 있다.

I/O 프로세서

- I/O 장치들의 동작을 제어하면 DMA 동작도 지원하는 프로세서로서, I/O 채널이라고도 부른다.

IOP가 지니고 있는 하드웨어들

- I/O 제어 프로그램을 수행할 수 있는 프로세서

- 데이터 블록을 임시 저장할 수 있는 용량의 지역 기억장치(local memory)

- 시스템 버스 인터페이스 및 버스 마스터 회로

- I/O 버스 인터페이스 및 중재 회로

IOP가 데이터 입출력을 위한 모든 동작들을 지원하게 됨에 따라, CPU는 I/O 동작에 대한 부담을 거의 가지지 않게 되었다.

- 특히 IOP는 프로세서와 내부 기억장치도 포함하고 있기 때문에, 운영체제(OS)의 I/O 장치 드라이버(I/O device driver) 프로그램들을 수행할 수 있다.

- 결론적으로 시스템 구성을 I/O 프로세서가 사용된 시스템의 구성도를 사용하면 성능이 크게 향상될 수 있다.

Reference

컴퓨터 구조론 개정 5판

07장 시스템 버스, I/O 및 인터럽트

7.1 시스템 버스 시스템 버스 : 컴퓨터 시스템의 구성 요소들을 상호 연결해주는 중심 통로 7.1.1 시스템 버스의 조직 버스 : 구성 요소들간에 교환할 각종 정보들을 전송하는 선들로 구성 시스템

velog.io

'CS > 컴퓨터 구조론' 카테고리의 다른 글

| 컴퓨터 구조론 8장 [고성능 컴퓨터시스템 구조 / 병렬컴퓨터의 분류] (0) | 2025.04.22 |

|---|---|

| 컴퓨터 구조론 8장 [고성능 컴퓨터시스템 구조 / 병렬처리의 개념 및 필요성, 병렬처리의 단위] (0) | 2025.04.22 |

| 컴퓨터 구조론 7장 [시스템 버스, I/O 및 인터럽트 /인터럽트를 이용한 I/O] (0) | 2025.04.21 |

| 컴퓨터 구조론 7장 [시스템 버스, I/O 및 인터럽트 / I/O 장치의 접속] (0) | 2025.04.21 |

| 컴퓨터 구조론 7장 [시스템 버스, I/O 및 인터럽트 / 버스 중재] (0) | 2025.04.19 |